이번 포스팅에서는 MOS를 실제상황을 고려하여 이상적인 경우와 C-V특성이 얼마나 달라지는지 알아보도록 한다.

우리가 지금까지 알아본 MOS의 다양한 특성들은 이상적인 경우만을 고려한 것이다.

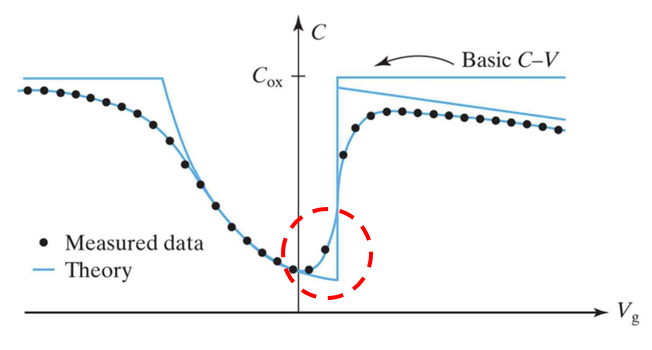

그렇다면 비이상적 효과를 고려한 C-V 특성은 어떻게 될까

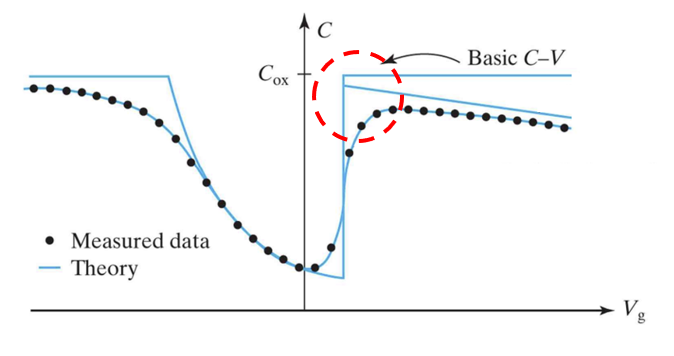

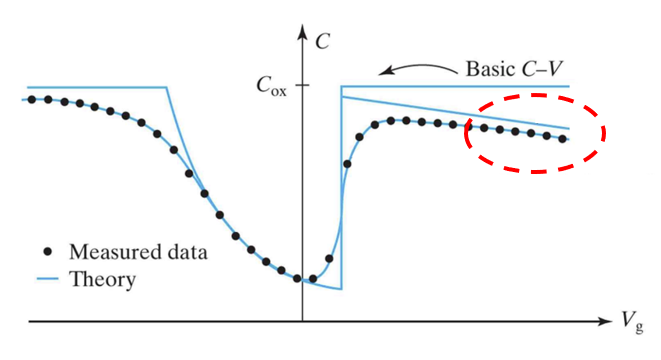

위의 C-V 특성 그래프는 ideal한 경우와 non-ideal한 경우의 그래프를 겹쳐서 그린것이다.

그렇다면 어떤 비이상적인 특성들로 인해 C-V 특성이 위와 같이 변하는지 알아보자.

1. Oxide Charge

우리는 지금까지 Flat Band 상황에서 반도체 내의 Charge는 0이라고 했다.

그렇다면 금속에 대응하는 charge가 존재하지 않는 문제가 발생한다.

실제 상황에서는 금속에 대응하는 charge가 존재한다.

그것이 바로 Oxide Charge($Q_{ss}'$)이다.

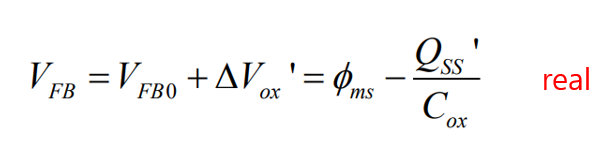

Oxide Charge로 인해 기존의 $V_{FB0}=\phi_{ms}$ (ideal)은

위와 같이 $V_{FB0}$가 Oxide Charge에 영향을 받는다.

Oxide Charge로 인해 $V_{FB0}$더 작아지게 된다.

Flat Band가 형성되는 시점이 더 빨라진다고 할 수 있다.

또한 Oxide Charge 로 인해 바뀐 $V_{FB0}$는 Thermal Voltage $V_T$에도 영향을 미친다.

2. QM effect in accumulation

accumulation 모드에서는 hole이 surface쪽에 매우 근접해서 몰려있다고 가정했다.

이로 인해 금속의 표면 charge과 반도체의 표면 charge로 인해 Capacitace는 $C_{ox}$라고 가정했다.

하지만 hole이 구덩이에 빠져 surface쪽에 몰리게 되면 hole은 infinite potential well에 갇히게 된 것과 같고,

이는 물리전자공학 시간에 배운 것에서 infinite potential well의 carrier의 농도는 양쪽 끝에서 0이라는 것을 알 수 있다.

그로 인해 사실 hole은 표면에 붙어 있는 것이 아닌,표면에 일정한 거리($t_{acc}$)만큼 떨어져 있다.

이것이 QM(quantum-mechanical effect) effect이다.

QM effect에 의한 capacitance는 hole이 경계면에서 떨어진 거리만큼 발생하는 추가적인 capactiance성분이 발생한다.

따라서 추가적인 capacitance성분이 직렬 연결된 것 처럼 영향을 미치기 때문에 전체 capactiance는 아래와 같다.

3. $Q_{inv}$ in depletion mode

우리는 지금까지 inversion에 의한 $Q_{inv}$을 $V_T$시점부터 고려했었다.

하지만 $Q_{inv}$은 $V_T$시점부터 존재하는 것이 아니라 $V_G$>0부터 생기며 점점 증가한다.

$V_G<V_T$ 에서는 그 양이 미미해서 고려하지 않았다.

$Q_{inv}$을 고려해보자.

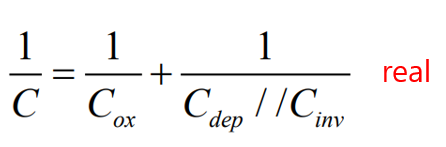

그러면 위와 같이 $Q_{inv}$과 $Q_{dep}$가 같이 존재한다고 하면

capacitance는 위와 같이 $C_{ox}+C_{inv}//C_{dep}$로 나타낼 수 있다.

$V_G$가 작을 때는 $C_{inv}$의 영향이 거의 미미 하지만 $V_T$에 근접하면, 무시할 수 없는 $C_{inv}$에 의해 capacitance값이 증가한다.

4. QM effect in strong inversion

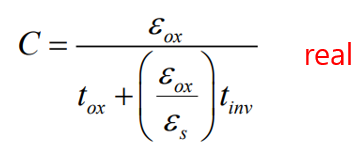

accumulation 모드와는 반대로 strong inversion에서는 electron이 surface쪽에 모이게 된다.

또한, 금속의 표면 charge와 반도체의 표면 electron charge로 인해 Capacitace는 $C_{ox}$라고 가정했다.

구덩이에 빠진 electro은 infinite potential well에 갇히게 된 것과 같게 되고,

$t_{inv}$거리만큼 떨어진 위치에 분포하게 된다.

5. Poly depletion in strong inversion

금속이 아니라 $n^+$ poly-si을 gate 전극으로 사용한다면 어떻게 될까

n형 si에 $V_G(>>V_T$)을 인가하면 electron들은 bulk쪽으로 이동해 depletion region이 형성된다. 이는 $C_{dep}'$을 형성한다.

$V_G$가 점점 커질수록 depletion region은 넓어지기 때문에 $C_{dep}'$은 감소한다.

Poly depletion에 의한 capacitance는 $C_{dep}'$ 만큼 더해진다. 이때 $V_G$가 증가하면 $C_{dep}'$ 점점 감소해 총 C도 감소하게 된다.

이번 포스팅에서는 비이상적 효과들에 의한 MOS capacitor의 실제적인 C-V특성 변화에 대하여 알아보았다.

C-V특성을 잘 분석하면 반도체 소자 동작특성 원리 탐구시 MOS에서 일어나는 많은 현상들을 파악할 수 있다는 점을 들어 비이상적효과들에 대한 공부도 굉장히 중요하다.

작성자: 김현수 / 수정 및 검토: 손동휘, 이현우

'Semiconductor > 기초반도체공학' 카테고리의 다른 글

| <MOSFET> 2. MOSFET 동작영역 (operation region) (4) | 2023.02.19 |

|---|---|

| <MOSFET>1. MOSFET 정성적 해석, 동작원리 (0) | 2023.02.19 |

| <MOS> 4. Capacitance-Voltage 특성 (0) | 2023.02.19 |

| <MOS> 3. Operation modes 수식 유도 (0) | 2023.02.19 |

| <MOS> 2. Parameter & gate bias (2) | 2023.02.19 |

댓글